An ADeLe use case

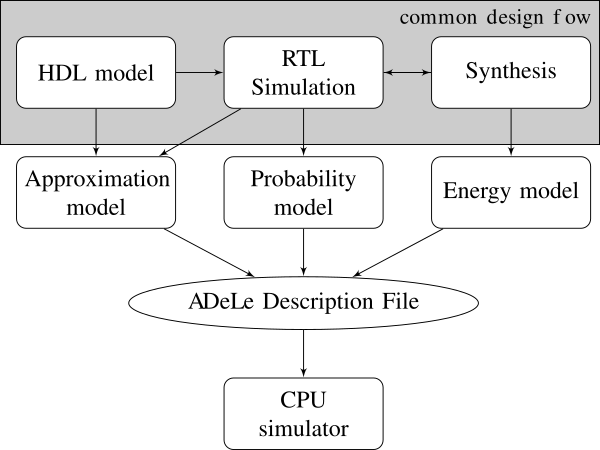

Our example targets a designer who wants to evaluate the impact of a new register bank design, powered by an adjustable supply voltage. In the typical hardware development flow, the designer would model the hardware using a Hardware Description Language (HDL), evaluate it in a Register Transfer Level (RTL) simulator and synthesize it to obtain power and timing data, back annotating this information to the netlist for further simulation. At this point, the designer has data on how the register bank behaves under different voltage levels and characterization of soft errors when reading and writing data to certain locations, as well as their occurrence distribution. In the context of Approximate Computing, errors under overscaled supply voltages may be seen as approximations that trade accuracy for energy savings in the computation.

The HDL model and RTL simulation data alone cannot provide any information about how the new design impacts real applications. A CPU simulator may help in evaluating and validating the design, and its integration in a system. Nevertheless, extensive effort would be required to adapt the simulator in order to inject code that represents the faulty register bank, to develop a control mechanism that parameterizes it according to the supply voltage, and to aggregate the results of RTL simulation to represent energy metrics.

The design flow

ADeLe proposes an enhanced design flow, that eliminates the effort of modifying the CPU simulator source code directly. Taking, as inputs, a generic model of the approximation and a high-level description of how it interacts with the target CPU model, an ADeLe-compatible CPU simulator automatically modifies its execution flow to represent the approximated behavior.

The ADeLe design flow requires three models: the instruction model describes the black-box behavior of the approximation at instruction-level, in terms of its input data and output results; the probability model defines whether the described behavior should happen instead of the default execution behavior in the simulator; and the energy model computes how much energy was spent to execute the instruction.

Modeling the approximated register bank

In our use-case scenario described at the beginning of this Section, the designer would implement the approximation model as a method that takes as input the handled data and outputs it with some random modification, modeling the unexpected bit flips perceived during RTL simulation when the register bank is powered by a lower supply voltage – in the ADeLe language, such an approximation model is called data modifier.

DM RandomBitFlip(source_t source, word &data) {

int bit = rand() % (8 * sizeof data);

data = data ^ (0x1 << bit);

}

The designer then writes a probability model that decides, from the current register bank supply voltage, whether the bit flips would happen on the data or not. The probability simply returns a boolean indicating that, and the current supply voltage may be defined as an operating parameter.

PM LowVddProb() {

return MagicVoltageToBool(OP['voltage']);

}

The energy model defines how much energy, in Joules, one single instruction execution uses. Since we are not interested in exact figures at this point, but in knowing how much savings we get, this can be simply translated as an scaling factor, another operating parameter.

EM SimpleEnergy() {

return OP['scaling'];

}

The ADeLe Description File

Finally, an ADeLe Description File is needed to link the models. The ADeLe Description File declares the three needed models, defines the operating parameters for each state (the different voltages and scalings) and when the models should be instantiated.

DM RandomBitFlip();

PM LowVddProb();

EM SimpleEnergy();

OP default_op = {.voltage = 1.0, // V

.scaling = 1.0}; // Scalar

OP low_vdd_op = {.voltage = 0.8, // V

.scaling = 0.6}; // Scalar

energy = SimpleEnergy();

parameters = default_op;

approximation LOW_VDD_REGBANK {

parameters = low_vdd_op;

regbank_read = RandomBitFlip();

regbank_write = RandomBitFlip();

probability = LowVddProb();

}